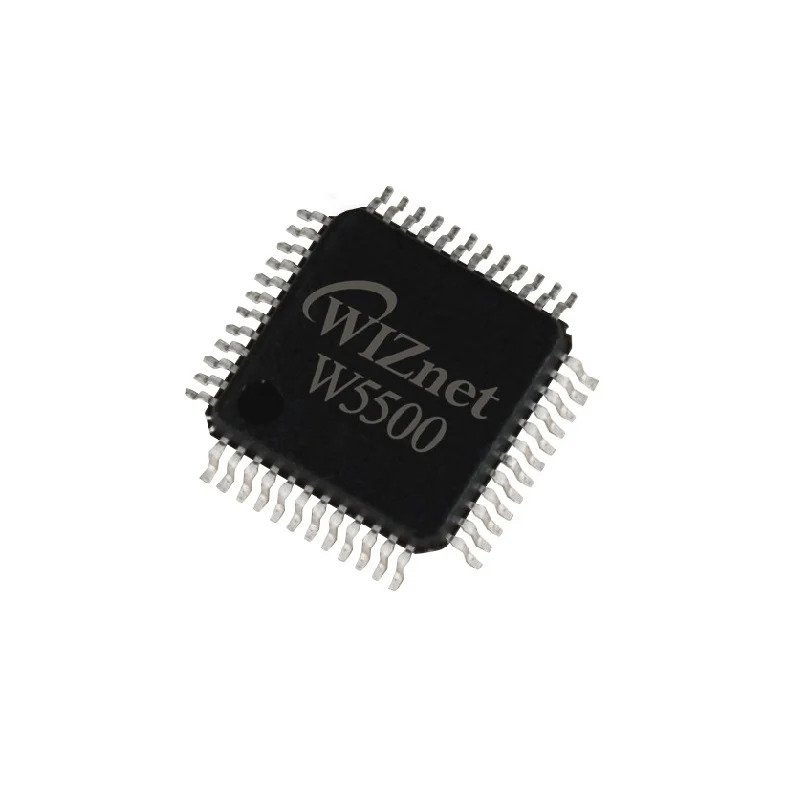

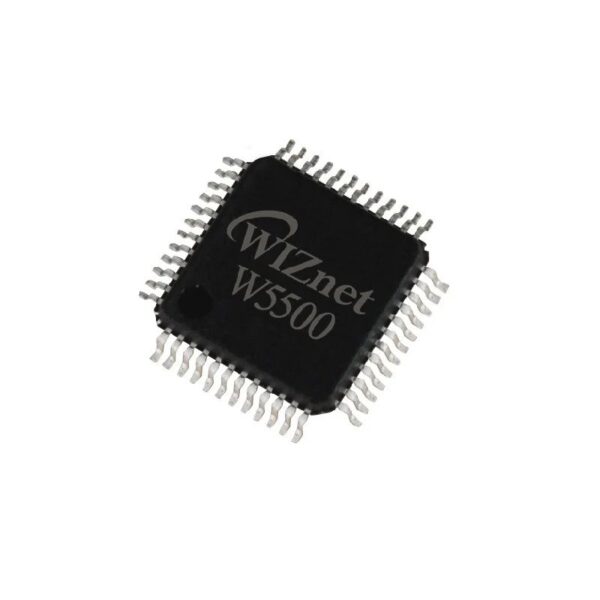

The W5500 chip is a Hardwired TCP/IP embedded Ethernet controller that enables easier internet connection for embedded systems using SPI (Serial Peripheral Interface).

W5500 suits users in need of stable internet connectivity best, using a single chip to implement TCP/IP Stack, 10/100 Ethernet MAC and PHY. Hardwired TCP/IP stack supports TCP, UDP, IPv4, ICMP, ARP, IGMP, and PPPoE, …, which has been proven through various applications over many years. W5500 uses a 32Kbytes internal buffer as its data communication memory.

Specifications:

- Operating Voltage: 3.3V operation with 5V I/O signal tolerance

- Memory: Internal 32Kbytes Memory for Tx/Rx Buffers

- IP Fragmentation: No

- LED outputs: (Full/Half duplex, Link, Speed, Active)

Features:

- Supports following Hardwired TCP/IP Protocols : TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE

- Supports 8 independent sockets simultaneously

- Supports Power down mode

- Supports Wake on LAN over UDP

- Supports High Speed Serial Peripheral Interface(SPI MODE 0, 3)

- Internal 32Kbytes Memory for Tx/Rx Buffers

- 10BaseT/100BaseTX Ethernet PHY embedded

- Support Auto Negotiation (Full and half duplex, 10 and 100-based)

- Not support IP Fragmentation

- 3.3V operation with 5V I/O signal tolerance

- LED outputs (Full/Half duplex, Link, Speed, Active)

Package Includes:

- 1 x WIZnet W5500